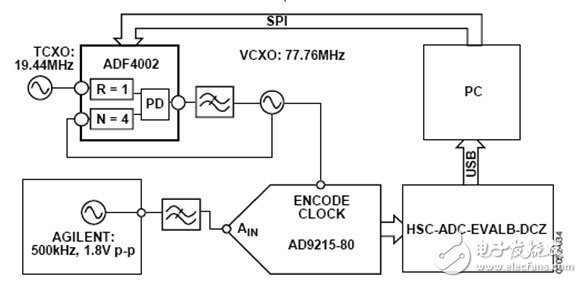

Circuit function and advantage This circuit uses the ADF4002 frequency synthesizer to generate very low jitter coded (sampled) clocks to control the sampling of the analog-to-digital converter AD9215. The jitter on the encoded clock reduces the total signal-to-noise ratio (SNR), as shown in the following equation: Where f is the full-scale analog input frequency and tj is the rms jitter. The "SNR" in Equation 1 is the SNR determined only by the clock jitter, independent of the resolution of the ADC. Circuit description The ADF4002 consists of a low noise digital phase frequency detector (PFD), a precision charge pump, a programmable reference divider, and a programmable N divider. The 14-bit reference counter (R counter) allows the REFIN frequency at the PFD input to be an optional value. If the frequency synthesizer is used with an external loop filter and voltage controlled oscillator (VCO), a complete phase-locked loop (PLL) can be implemented. Figure 1 shows that the ADF4002 and VCXO together provide an encoding clock for high speed analog-to-digital converters. The converter in this application is a 10-bit converter, the AD9215-80, which accepts encoded clocks up to 80 MHz. To achieve a stable low jitter clock, a 77.76 MHz narrowband VCXO is used. This example assumes a reference clock of 19.44 MHz. To minimize the phase noise contribution of the ADF4002, a minimum multiplication factor of 4 is used. Therefore, the R divider is programmed to 1 and the N divider is programmed to 4. The charge pump output (Pin 2) of the ADF4002 drives the loop filter, and the bandwidth of the loop filter is optimized to provide optimal rms jitter, which is a key factor in determining the signal-to-noise ratio of the ADC. If the bandwidth is too narrow, VCXO noise dominates at a small frequency offset relative to the carrier frequency. If the bandwidth is too wide, the ADF4002 noise will dominate the frequency offset where the VCXO noise is lower than the ADF4002 noise. Therefore, the optimal bandwidth of the loop filter corresponds to the intersection of VCXO noise and the ADF4002 in-band noise. Figure 1. ADF4002 used as an encoding (sampling) clock for high speed ADCs The loop filter can be designed using the ADIsimPLLTM design tool (version 3.0), which is available for free download at analog.com/pll. The measured rms jitter is less than 1.2 ps. Assuming the input signal is 20 MHz, the theoretical value of SNR (determined only by jitter) is 76.4 dB using Equation 1 above. This value is 17.4 dB higher than the ADC's nominal SNR (59 dB), resulting in a total SNR reduction of only 0.1 dB. If the rms jitter is increased to 6 ps, the corresponding SNR determined by jitter at 20 MHz is 62.4 dB, resulting in a total SNR of 57.4 dB. For accurate measurements, a low noise, low distortion analog input source is required. This is achieved by using a high quality signal generator and a bandpass filter that is tuned to the target frequency. Although the 500 kHz source is shown in Figure 1, it should be able to test higher frequency sources. A separate bandpass filter is required for each additional frequency. The setup shown in Figure 1 uses the ADF4002, AD9215, and HSC-ADC-EVALB-DCZ to allow the user to quickly and efficiently determine if the converter and code clock are appropriate. The SPI interface is used to control the ADF4002, and the USB interface helps control the operation of the AD9215-80. The controller board sends the FFT information back to the PC. If the PC uses Analog Devices' ADC AnalyzerTM software, it will provide all conversion results from the ADC. In order to achieve the required performance, the entire system must use excellent layout, grounding and decoupling techniques. Common changes A PLL-based clock generation circuit, as shown in Figure 1, is often used to generate a clean, low-jitter clock from a high-noise system clock. Analog Devices offers many different frequency synthesis and clock generation products for similar applications. Car Screen Protector,Car Center Console Screen Protector,Car Touchscreen Screen Protector Shenzhen Jianjiantong Technology Co., Ltd. , https://www.jjtscreenprotector.com